# HDMI\_HT3 EH1706003017 Reference Manual

March 2018 ver0.1

# **Copyright Notice and Proprietary Information**

© 2018 E-elements Technology Co., Ltd. These all associated documentation are proprietary to E-elements and may only be used pursuant to the terms and conditions of a written license agreement with E-elements. All other use, reproduction, modification, or distribution of the associated documentation is strictly prohibited.

# **Third-Party Links**

Any links to third-party websites included in this document are for your convenience only. E-elements does not endorse and is not responsible for such websites and their practices, including privacy practices, availability, and content.

E-ELEMENTS TECHNOLOGY CO., LTD.

5F, No.61, Lane76, RuiguangRd.,

Neihu Dist., Taipei,

Taiwan, R.O.C.

www.e-elements.com

# **Revision History**

| Date     | Rev | Comment         |

|----------|-----|-----------------|

| Mar 2018 | v0  | Initial version |

| Nov 2018 | v1  | HDMI Pin        |

# Contents

| Revision History4    |

|----------------------|

| HDMI_HT3 IMPORTANT!6 |

| Overview             |

| Layout8              |

| Block Diagram9       |

| Card Placement       |

| HDMI Transmitter11   |

| Clocks               |

| Pin Tables13         |

# HDMI\_HT3

#### IMPORTANT!

#### **ESD**

The HAPS®SOC\_NORF\_HT3 Transceiver Card, as with all other electronic equipment, is sensitive to electrostatic discharge (ESD). When handling the transceiver card:

- •Transport the card in an ESD bag

- •Wear an anti-static wrist strap

- •Make sure the work area is equipped with an ESD mat

#### Warning

Never hot-plug interface cards, daughter boards or cables. Always power down the HAPS system when adding or removing a board, card, or cable to avoid damage to both the system and peripheral.

### HapsTrak® 3 Connector Considerations

The HT3 connectors must be attached carefully! If connected improperly socket pins can be deformed or holding rail ends can become damaged.

When connecting daughter boards and HT3 cable connectors, they should be held parallel to the SOC\_NORF\_HT3 connector throughout the mating process.

Overview HDMI\_HT3

# Overview

This document is the HDMI\_HT3 Reference Manual and describes the functions of the HDMI\_HT3 daughter board.

The HDMI\_HT3 daughter board may be set up for configure HDMI Transmitter through HT3. Offer input data for HDMI video out.

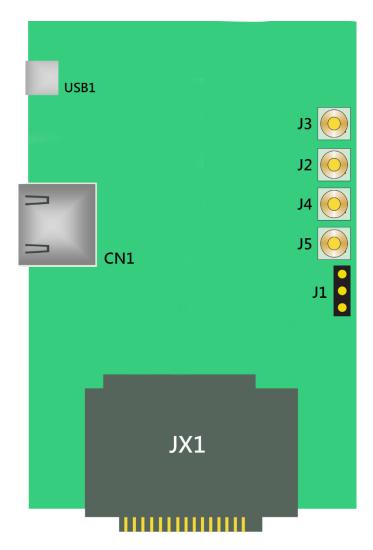

Figure 1: Top View of HDMI\_HT3

Overview HDMI\_HT3

# HDMI\_HT3 daughter board consists of:

- 1 HT3 Connector, Power

- 1 HDMI 1.4 Connector

- 1 USB-Micro-B Connector

- 2 pairs of Differential MMCX Clock Connectors (for Global Clocks)

Layout HDMI\_HT3

# Layout

Figure 2: HDMI\_HT3 Layout

Block Diagram HDMI\_HT3

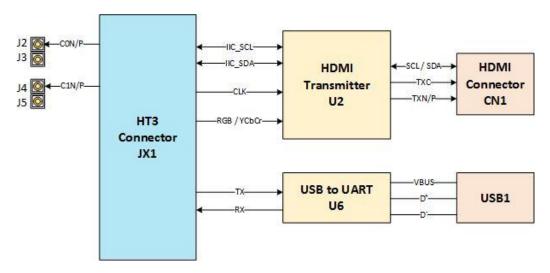

# **Block Diagram**

Figures 3 show the connectivity between the HDMI\_HT3 daughter board's HDMI connector and connectors to the HT3 connector. The HT3 I/O pin mapping is described in the JX1 pin table on page 13.

Figure 3: HDMI\_HT3 Block Diagram

Card Placement HDMI\_HT3

# Card Placement

#### HAPS-80

HAPS-80 systems include 24 HT3 Connector for each FPGA. The HapsTrak 3 (HT3) is a 160-pin connector containing 52 signal pins, most of which can be used for single ended or differential signaling. All signals in a connector are associated with the same FPGA I/O bank voltage (VCCO). The I/O voltage dictates which electrical I/O standards can be used for the signal pins.

The HDMI\_HT3 daughter board may be set up by HT3. Figure 4 shows an example setup with a HAPS-80 system.

Figure 4: HDMI\_HT3 mounted on HAPS-80 system

HDMI Transmitter HDMI\_HT3

# **HDMI** Transmitter

The ADV7511 is a 225 MHz High-Definition Multimedia Interface transmitter located at U2. Supports the HDMI 1.4-specific features, HEAC (ARC), and 3D video. allows the secure transmission of protected content as specified by the HDCP 1.4 protocol.

The ADV7511 accepts video data from as few as eight pins (either YCbCr 4:2:2 double data rate [DDR] or YCbCr 4:2:2 with 2x pixel clock) or as many as 36 pins (RGB 4:4:4 or YCbCr 4:4:4). In addition it accepts HSYNC, VSYNC and DE (Data Enable).

| 14-1-  |        | Input Data D[35:0] 35   34   33   32   31   30   29   28   27   26   25   24   23   22   21   20   19   18   17   16   15   14   13   12   11   10   9   8   7   6   5   4   3   2   1   0 |       |    |    |                         |       |          |                              |  |  |  |

|--------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----|----|-------------------------|-------|----------|------------------------------|--|--|--|

| Mode   | гогшаг | 35 34 33 32 31 30 29 28 2                                                                                                                                                                  | 27 26 | 25 | 24 | 23 22 21 20 19 18 17 16 | 15 14 | 13       | 3 12 11 10 9 8 7 6 5 4 3 2 1 |  |  |  |

| 36     | RGB    | R[11:0]                                                                                                                                                                                    |       |    |    | G[11:0]                 |       | B[11:0]  |                              |  |  |  |

| bit    | YCrCb  | Cr[11:0]                                                                                                                                                                                   |       |    |    | Y[11:0]                 |       | Cb[11:0] |                              |  |  |  |

| 30     | RGB    | R[9:0]                                                                                                                                                                                     |       |    |    | G[9:0]                  |       |          | B[9:0]                       |  |  |  |

| bit    | YCrCb  | Cr[9:0]                                                                                                                                                                                    |       |    |    | Y[9:0]                  |       | Cb[9:0]  |                              |  |  |  |

| 24     | RGB    | R[7:0]                                                                                                                                                                                     |       |    |    | G[7:0]                  |       |          | B[7:0]                       |  |  |  |

| bit    | YCrCb  | Cr[7:0]                                                                                                                                                                                    |       |    |    | Y[7:0]                  |       |          | Сь[7:0]                      |  |  |  |

| Pins I | [35:0] | 35 34 33 32 31 30 29 28 2                                                                                                                                                                  | 27 26 | 25 | 24 | 23 22 21 20 19 18 17 16 | 15 14 | 13       | 3 12 11 10 9 8 7 6 5 4 3 2 1 |  |  |  |

Table 1: Normal RGB or YCbCr 4:4:4 with Separate Syncs; Input ID = 0

Clocks HDMI\_HT3

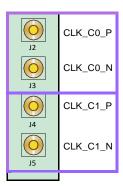

# Clocks

MMCX connectors for clock connection between the user FPGA and other components in a hardware setup.

| MMCX<br>Connector | Differential<br>or Single- ended | Direction | Source or Destination |         |  |  |

|-------------------|----------------------------------|-----------|-----------------------|---------|--|--|

| J2/J3             | DIFF                             | Output    | C                     | COP/CON |  |  |

| J4/J5             | DIFF                             | Output    | Source                | C1P/C1N |  |  |

Table 2: MMCX Clock Connections

## **Output Clocks**

Output clocks are internal signals (FPGA generated clocks or HAPS global clocks) that travel from the HAPS system through the HDMI\_HT3 daughter board.

Access to the HAPS system's differential global clock (GCLK) signals are available through the Output clock SMB connector pairs on the HDMI\_HT3 daughter board. Table 2 is a list of clock connections for each MMCX connector.

Figure 5: DIFF Clocks

# Pin Tables JX1

| JAT |                         |               |            | 7571 |     |                      |    |      |     |  |

|-----|-------------------------|---------------|------------|------|-----|----------------------|----|------|-----|--|

|     |                         |               |            |      |     |                      |    |      |     |  |

| Pin | Trace Name              | Connector Pin |            |      |     | Trace Name Connector |    |      |     |  |

| A0  | HDMI INT                |               | omice to i |      | C0  | HDMI D14             |    |      |     |  |

| A1  | IIC SCL HDMI            |               |            | -    | C1  | HDMI D13             | U2 |      |     |  |

| A2  | HDMI D31                |               |            |      | C2  | HDMI D8              |    | vcco |     |  |

| A3  | HDMI D30                |               |            |      | C3  | HDMI D7              |    |      |     |  |

| A4  | IIC_SDA_HDMI            | 1             |            |      | C4  | HDMI_D12             |    |      |     |  |

| A5  | HDMI_D35                | 110           | vcco       |      | C5  | HDMI_D11             |    |      |     |  |

| A6  | HDMI_D29                | U2            |            |      | C6  | HDMI_D6              |    |      |     |  |

| A7  | HDMI_D28                | 1             |            |      | C7  | HDMI_D5              |    |      |     |  |

| A8  | HDMI_D34                | 1             |            |      | C8  | HDMI_D10             |    |      |     |  |

| A9  | HDMI_D33                | 1             |            |      | C9  | HDMI_D9              |    |      |     |  |

| A10 | HDMI_D27                |               |            |      | C10 | HDMI_D4              |    |      |     |  |

| A11 | HDMI_D26                |               |            |      | C11 | HDMI_D3              |    |      |     |  |

| A12 |                         |               |            |      | C12 |                      |    |      |     |  |

| A13 |                         |               |            |      | C13 |                      |    |      |     |  |

| B0  | HDMI_D25                |               |            |      | D0  | HDMI_D2              | U2 | vcco |     |  |

| B1  | HDMI_D24                |               |            |      | D1  | HDMI_D1              | 02 | VCCO |     |  |

| B2  | HDMI_D19                |               |            |      | D2  | USB_UART_TX          | U6 | VCCO |     |  |

| B3  | HDMI_D18                |               |            |      | D3  | USB_UART_RX          | 00 | VCCO |     |  |

| B4  | HDMI_D23                |               |            |      | D4  | HDMI_D0              | U2 | VCCO |     |  |

| B5  | HDMI_D22                | U2            | VCCO       |      | D5  | HDMI_DE              | 02 | VCCO |     |  |

| B6  | HDMI_D17                | 02            | VCCO       |      | D6  | JX1_D6               | J1 | VCCO |     |  |

| B7  | HDMI_CLK                |               |            |      | D7  | HDMI_D32             |    |      |     |  |

| B8  | HDMI_D21                |               |            |      | D8  | HDMI_HSYNC           |    |      |     |  |

| B9  | HDMI_D20                |               |            |      | D9  | HDMI_VSYNC           | D4 | 3.3V |     |  |

| B10 | HDMI_D16                |               |            |      | D10 | HDMI_SPDIF           |    |      |     |  |

| B11 | HDMI_D15                |               |            |      | D11 | HDMI_SPDIF_OUT_LS    |    |      |     |  |

| B12 |                         |               |            |      | D12 |                      |    |      |     |  |

| B13 |                         |               |            |      | D13 |                      |    |      |     |  |

|     |                         |               |            |      | C0N | CLK_C0_N             | J2 | VCCO |     |  |

|     | U2 HDMI                 |               |            |      | C0P | CLK_C0_P             | J3 | VCCO | DIE |  |

|     | U6 UART                 |               |            |      | C1N | CLK_C1_N             | J4 | VCCO | DIF |  |

|     | J1 GPIO                 |               |            |      | C1P | CLK_C1_P             | J5 | VCCO |     |  |

|     | J2/J3/J4/J5 Differentia | al Clock      |            |      |     |                      |    |      |     |  |