設計驗證

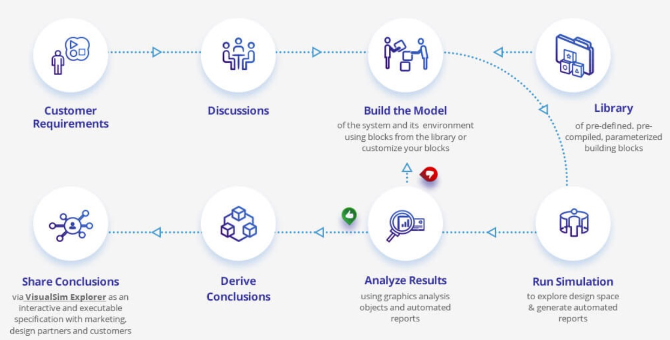

系統及單晶片架構探索以及設計驗證平台,不僅免去了構建模型的工程,同時也加速了複雜設計的模擬。確保模型正確性,大幅縮短產品開發時長。

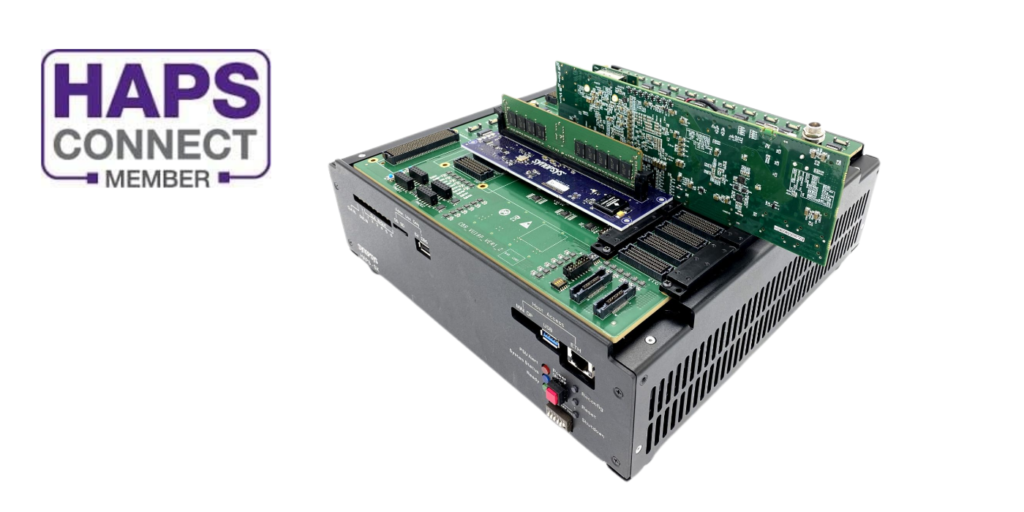

隨著芯片集成度提高和性能的多元化, 大規模集成電路設計複雜性的提升,使芯片驗證面臨巨大挑戰。基於Xilinx可編程邏輯門陣列(FPGA)建立有效的原型驗證平台已成為晶片開發設計驗證的主要選擇。 而原型驗證需要使用的子板種類多樣,很多時候需要客製化設計,進一步給調試帶來了不確定性,也延長了調試週期。一元素科技提供基於新思科技HAPS原型驗證解決方案, 給用戶提供了多種靈活的接口方案,包含豐富的外部子卡集合,降速與同步方案, 並通過HAPS Connect Program,為使用者提供了更廣泛的擴展空間

- Customized and integrated Synopsys MIPI IP with SMF board to work with HAPS prototyping system

- Customized HT3 daughter board design with Intel IP to validate on HAPS prototyping system

- Validated PCIeGen5 32G on HAPS prototyping system

- Evaluation board with DM.2 on HAPS Zebu system

系統及單晶片架構探索以及設計驗證平台,不僅免去了構建模型的工程,同時也加速了複雜設計的模擬。這種作法讓團隊不用花費大量的時間和精力在建立複雜設計的模型上,對於基於模型設計方法的設計項目而言,這不僅確保了模型的正確性,也大幅縮短了產品開發時長。 系統層級自動化設計工具包含:軟體自動化設計模擬軟件、豐富模型庫

Functional correctness, speed, topology and arbitration

Quality, traffic stimulus, impact of configuration and power

Throughput, response time, Buffer size and utilization

Peak and average power, energy and power/task

ISO-26262 and RO-254 certifications